- 您现在的位置:买卖IC网 > Sheet目录1998 > ICS87159AGLFT (IDT, Integrated Device Technology Inc)IC CLOCK GEN 1-8 LVCMOS 56-TSSOP

87159AG

www.idt.com

REV. B JULY 25, 2010

10

ICS87159

1-TO-8 LVPECL-TO-HCSL

÷1, ÷2, ÷4 CLOCK GENERATOR

C1

10uf

C10

0.1uF

R8

28

(U1-34) (U1-40)

(U1-4)

Zo = 50

VDD

C7

0.1uF

Zo = 50

(U1-27)

C2

0.1uF

R3

33

VDD

(U1-2)

C5

0.1uF

(U1-46)

Zo = 50

nPCLK

Parallel Termination

(U1-5)

C3

0.01uF

PCLK

C6

0.1uF

C8

0.1uF

Receiver

PCI Express Termination

C4

0.1uF

Receiver

(U1-16)

R4

50

R6

33

Zo = 50

VDD

C13

0.1uF

Zo = 50

C2

0.1uF

Zo = 50

PCI Express Termination

should be as close the

device as possible

IREF

475

C11

0.1uF

(U1-15)

HCSL

+

-

C9

0.1uF

R18

50

(U1-21)

Optional Series Termination

R5

50

HCSL

+

-

(U1-9)

VDD

C1

0.1uF

U1

87159

1

2

3

4

5

6

7

8

9

10

43

44

33

35

36

40

39

37

11

12

13

14

15

16

17

18

19

20

21

22

23

24

34

38

41

42

50

49

48

47

46

45

54

53

52

51

55

56

25

26

27

28

32

31

30

29

GND_H

VDD_H

GND

VDD

VDD_R

PCLK

nPCLK

GND_R

VDD_M

MREF

GND_H

HOST_N4

IREF

HOST_N7

HOST_P7

VDD_H

HOST_P6

GND_H

nMREF

GND_M

VDD

GND

VDD_L

VDD

GND_L

SEL_T

MULT_0

MULT_1

VDD_L

GND_L

SEL_A

SEL_B

VDD_H

HOST_N6

HOST_N5

HOST_P5

HOST_N2

GND_H

HOST_P3

HOST_N3

VDD_H

HOST_P4

VDD

GND_H

VDD_H

HOST_P2

HOST_N1

HOST_P1

SEL_U

PWR_DWN#

VDD_H

GND_H

GND_I

VDD_I

HOST_P8

HOST_N8

(U1-52)

R1

100

(U1-31)

Optional Termination

C3

0.1uF

C14

0.1uF

R2

100

R17

50

(U1-52)

C15

0.1uF

C4

0.001uF

(U1-13)

C12

0.1uF

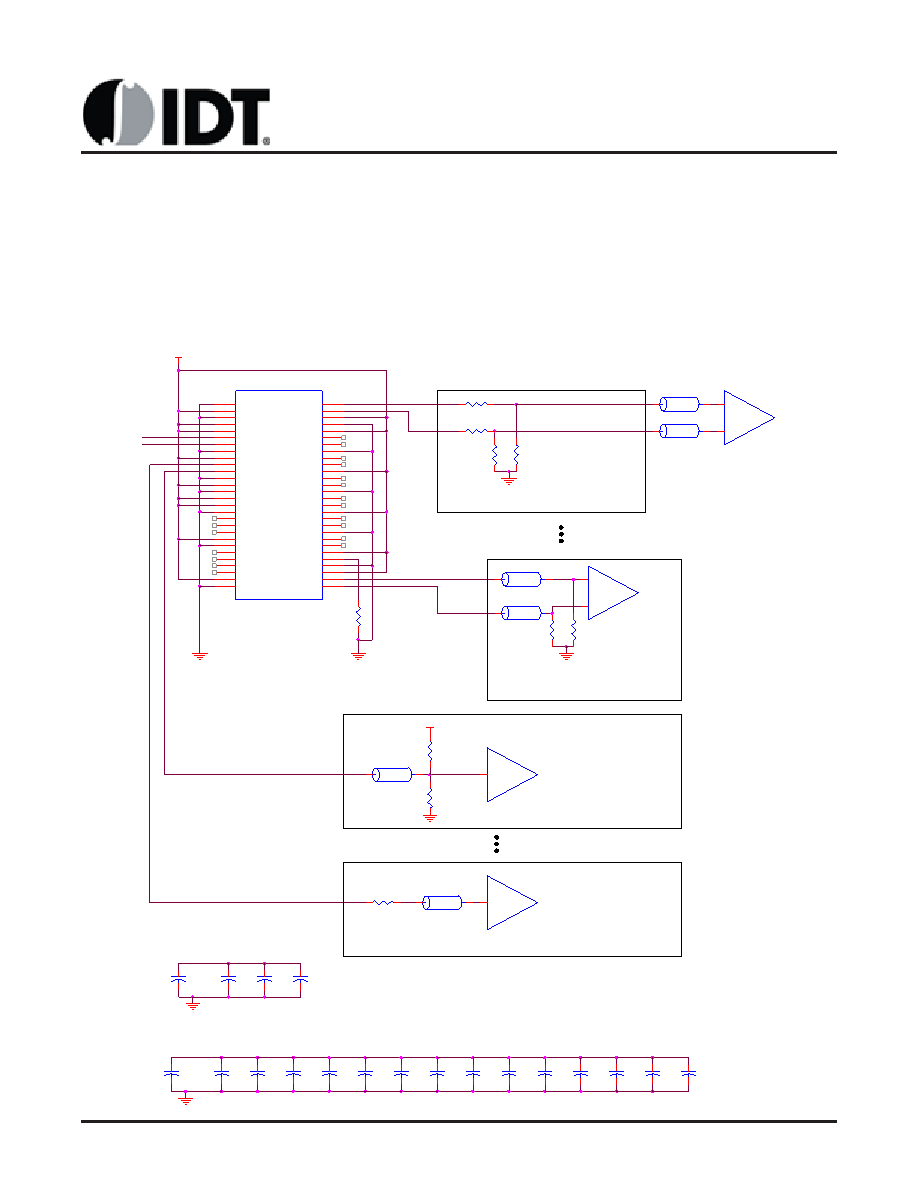

SCHEMATIC EXAMPLE

Figure 3 shows an example of the ICS87159 LVPECL to

HCSL Clock Generator schematic.

In this example, the ICS87159 is configured as follows:

PWR_DWN# = 1

Mult_[1:0] = 10, Rref = 475

Ω, IREF = 2.32mA, I

OH = 6*IREF

SEL_[A,B,U] = 000, MREF = PECL

÷ 4, all HOST outputs = PECL ÷ 2

SEL_T = 0, Output Enable

FIGURE 3. ICS87159 SCHEMATIC LAYOUT

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS8731CY-01LF

IC CLOCK ULT/ZD BUFFER 48-LQFP

ICS8732AY-01LF

IC CLK GEN LV 3.3V LVPECL 52LQFP

ICS87332AMI-01LFT

IC CLK GEN ECL/LVPECL 8-SOIC

ICS87354AMILF

IC CLK GEN 3.3V LVPECL 8-SOIC

ICS873995AYLF

IC ZD/MULT/DIVIDER 48-LQFP

ICS874001AGI-02LF

IC PCI EXPRSS/JITT ATTEN 20TSSOP

ICS874001AGI-05LFT

IC PCI EXPRSS/JITT ATTEN 20TSSOP

ICS874002AGLFT

IC PCI EXPRSS/JITT ATTEN 20TSSOP

相关代理商/技术参数

ICS871S1022EKLF

制造商:Integrated Device Technology Inc 功能描述:IC FEMTOCLOCK LVPE 32VFQFN

ICS871S1022EKLFT

制造商:Integrated Device Technology Inc 功能描述:IC FEMTOCLOCK LVPE 32VFQFN

ICS8725AM-21LF

功能描述:IC CLOCK GEN ZD HSTL 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND

ICS8725AM-21LFT

功能描述:IC CLOCK GEN ZD HSTL 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

ICS8725AY-01LF

功能描述:IC CLK GEN ZD 2:5 HSTL 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS8725AY-01LFT

功能描述:IC CLK GEN ZD 2:5 HSTL 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

ICS8725BY-01LF

制造商:Integrated Device Technology Inc 功能描述:

ICS873033AGLF

功能描述:IC CLK GENERATOR /4 DIFF 8-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG